Существует два способа построения схемы частотомера. В первом случае в течении счетного периода производится подсчет входных импульсов (при разрешении в 1 Гц счетный период составляет 1 секунду). В течении этого периода индикаторы либо погашены, либо мелькают, затем следует период индикации, который обычно тоже составляет 1 секунду. Таким образом, при разрешении в 1 Гц один измерительный цикл составляет 2 секунды. Согласитесь, это слишком много даже для радиолюбительской практики.

Второй метод отличается тем, что периоды измерения и индикации как бы наложены друг на друга. Пока идет период индикации предшествующего результата, происходит подсчет импульсов для определения будущего результата. В таком случае весь цикл измерения близок к одной секунде. Такой метод требует наличия ячеек памяти, в которые можно записывать результат предыдущего измерения и индицировать пока длится последующее. Частотомер построенный по этому принципу, просто с частотой в 1 Гц обновляет свои показания.

На первый взгляд, такой быстрый способ измерения организовать достаточно просто, нужно постоянно подавать входные импульсы на счетный вход декадного счетчика, и с периодичностью в 1 секунду подавать два коротких импульса, — один на вход записи ячеек памяти, а второй на вход R декадного счетчика. Реализовать все это очень просто, если по спаду импульса образцовой частоты 1 Гц формировать два последовательных коротких импульса. Такой способ имеет существенный недостаток. Дело в том что, длительности этих двух коротких импульсов фактически вычитаются из периода измерения, внося в результат измерения ошибку. Причем, если короткие импульсы сформированы RC-цепями, то эта ошибка еще получается и нестабильной.

Для того чтобы исключить эту ошибку, нужно схему устройства управления построить таким образом, чтобы спустя период измерения (1 секунду) закрывался вход частотомера, и только после этого были сформированы эти два коротких импульса. То есть, эти два коротких импульса нужно вынести за период измерения. Принципиальная схема входного узла и узла управления частотомера, работающего на таком принципе показана на рисунке.

Измеряемый сигнал через гнездо Х1 и разделительный конденсатор С1 поступает ограничительную цепь на диодах VD1-VD6 и резисторе R1. Эта цепь защищает вход усилителя на VT1 от перегрузки сигналом большой амплитуды. Транзистор VT1 включен по схеме истокового повторителя, и нагружен на дифференциальный усилитель, выполненный на двух транзисторах микросборки А1 и транзисторе VT2. Коэффициент усиления этого усилителя около 10. Режим работы дифференциального каскада задается делителем напряжения R7 R5. Подбирая сопротивление R3, включенное в истоковой цепи VT1, можно устанавливать максимальную чувствительность входного узла.

С коллектора VT2 усиленный сигнал поступает на формирователь импульсов — управляемый триггер Шмитта на элементах D1.1 и D1.2. Особенность этого триггера Шмитта в том, что его можно блокировать подачей логической единицы на вывод 5 D1.2. И таким образом, закрывать проход импульсов на счетный вход декадного счетчика.

Генератор образцовой частоты построен на специализированной микросхеме D2 К176ИЕ12, которая содержит элементы кварцевого мультивибратора и набор счетчиков-делителей. Частота мультивибратора устанавливается кварцевым резонатором Q1 (стандартный резонатор от электронных часов), и на выводе 4 счетчика микросхемы получаются импульсы частотой 1 Гц. Вывод 5 — это вход обнуления счетчика. Когда на него подается единица, на всех выходах, включая и вывод 4, будут нули. При подаче нуля на вход R (вывод 5), на выводе 4 сразу же появляется единица и формируется фронт первого из импульсов, следующих с частотой 1 Гц.

Импульсы с выхода D2 поступают на вход С D-триггера D3.1. Предположим, этот триггер находился в нулевом состоянии. Тогда единица с его инверсного входа закрывает элемент D1.2 и одновременно поступает на вход D триггера, подготавливая его к установке в единичное состояние. С первым же фронтом импульсы с вывода 4 D2 триггер принимает единичное состояние. Элемент D1.2 открывается и начинается подсчет импульсов входной частоты. В то же время, нуль с инверсного входа поступает на вход D триггера и подготавливает триггер к установке в нулевое состояние.

С поступление второго фронта с вывода 4 D2 (с завершением секундного периода), триггер устанавливается в нулевое состояние. При этом происходит следующее: закрывается элемент D1.2 и прекращается поступление импульсов на вход декадного счетчика. Затем, цепь С9 R14 формирует короткий импульс, который производит запись результата измерения в ячейки памяти дешифраторов декадного счетчика. Далее, спустя время распространения через два элемента D1.3 и D1.4, формируется еще один такой импульс, который одновременно обнуляет и декадный счетчик и счетчик микросхемы D2. Счетчик D2 обнуляясь на время действия этого короткого импульса меняет уровень на выводе 4 на нулевой, и затем, после окончания этого короткого импульса обнуления, на выводе 4 D2 снова появляется единица. Триггер D3.1 опять принимает единичное состояние и начинается новый цикл измерения.

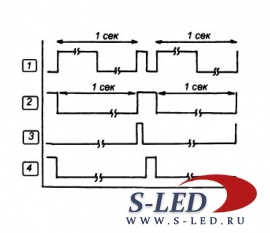

Рис. 2

Таким образом, D2 формирует не четкую импульсную последовательность частотой 1 Гц, а более сложную, в которой после каждого полного периода длительностью в 1 секунду, следует другой полный период очень короткой длительности. И именно в этом коротком периоде и происходит запись информации и обнуление декадного счетчика. А счет входных импульсов происходит в периоде длительностью в одну секунду. И длительность импульсов обнуления и записи не оказывает влияния на результат измерения.

Эпюры, описывающие работу узла управления приведены на рисунке 2.

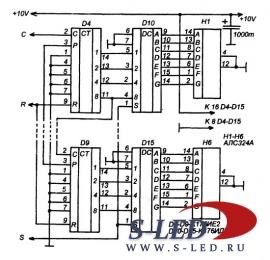

Рис. 3

Принципиальная схема узла декадных счетчиков показана на рисунке 3. Всего шесть разрядов (диапазон измерения от "000001" до "999999"). Шестидекадный счетчик составлен из шести микросхем К176ИЕ2 (D4-D9), каждая из которых включена по схеме декадного счета. Входные импульсы измеряемой частоты поступают на вход С D4. Шесть счетчиков включены последовательно. Обнуление счетчиков производится подачей короткого импульсы от RC-цепи С10 R15 на соединенные вместе входы R.

С выходов счетчиков коды десятичных чисел поступают на шесть дешифраторов К176ИД2 (D10-D15). Запись и обновление результата измерения в память дешифраторов выполняется подачей короткого импульса от RC-цепи С9 R14 на соединенные вместе входы S дешифраторов.

Индикация — при помощи шестиразрядного цифрового табло, составленного из шести семисегментных светодиодных цифровых индикаторов Н1-Н6. Индикаторы светятся постоянно, а их показания меняются с частотой, чуть меньше 1 Гц.

Светодиодные семисегментные индикаторы можно использовать любые одиночные, или комбинированные, но имеющие самостоятельные выводы сегментов (не объединенные в динамические матрицы). Полярность сегментов тоже существенного значения не имеет. В данной схеме используются индикаторы с общим катодом, поэтому на выводы 6 микросхем К174ИД2 подаются логические нули (это переключает микросхему на работу активными единицами на выходах). Если будут индикаторы с общими анодами, то логический уровень на выводах 6 D10-D15 нужно сменить на единицу (отключить от минуса питания и подключить на плюс).

Вместо дешифраторов К176ИД2 можно использовать и К176ИДЗ. Все микросхемы серии К561 можно заменить аналогичными микросхемами серии К176 или К1561. При отсутствии микросхем К176ИЕ2 можно применить К561ИЕ14, но схемы включения этих микросхем существенно различаются.

В настройке нуждается только входной узел. Нужно на вход (разъем Х1) подать синусоидальный сигнал частотой 1 МГц и амплитудой 1 В. К выходу элемента D1.2 подключить осциллограф. Затем, постепенно уменьшая уровень входного сигнала подобрать номинал резистора R4 таким, чтобы прямоугольность импульсов на экране осциллографа сохранялась при наименьшем сигнале.